Adressierung und Chipauswahl

Wie in Der Adressraum unseres 8-Bit Computer beschrieben, haben wir verschiedene Bereiche, in den wir verschiedene Arten von Speicherchips (RAM und ROM) ansprechen wollen.

Wie funktioniert das nun.

Adressierung

Für unseren Computer ist erstmal der komplette Speicherbereich der 64kB direkt abrufbar. Das passiert über die 16 Adressleitungen.

Der Wert der Adressleitungen entspricht dem Byte, was wir lesen oder schreiben wollen.

Wir haben uns aber noch nicht die Chips angeschaut, welche dann (simuliert) zu Einsatz kommen.

Grundsätzlich werden solche RAM oder ROM Chips als XXX kBit definiert, häufig auch in der Schreibweise z.B. 8K x 8 was bedeutet wir haben 8000 Adressen mit jeweils 8 Bit, also 8KB. es gibt auch

Chips mit z.B. 8K x 16 das sind dann 8000 mal 16 Bit, d.h. jede Adresse liefert 2 Bytes zurück. Das sind dann 16KB.

Dummerweise gibt es bei den einschlägigen Quellen keine Chips in 16K x 8. Also haben wir die Wahl aus 2x 8K x 8 oder 32K x 8.

Ich entscheide mich hier für Variante 2, auch wenn wir dann 16KB verschwenden. Bei Chipkosten von ~2,70€ ist das zu verschmerzen. Der (simulierte) Chip meiner Wahl für das RAM ist

der Alliance Memory AS6C62256-55PCN.

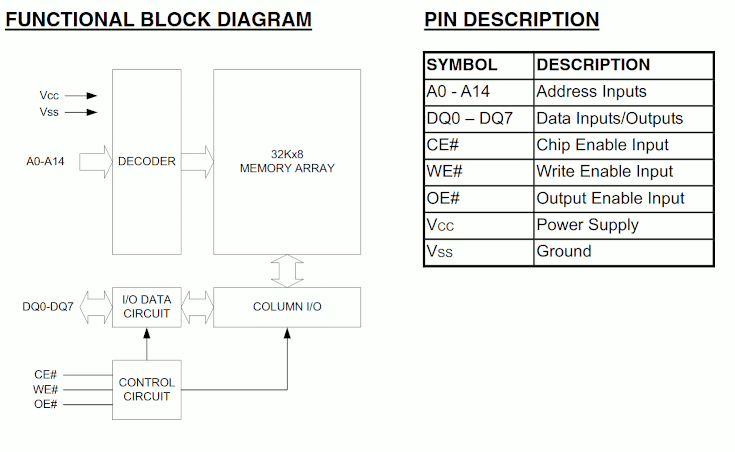

Ein Blick in das passende Datenblatt verrät uns unter anderem die Anschlüsse und das Blockschaltbild:

Da es sich um einen 32K Chip handelt, gibt es 15 Adressleitungen (215=32K), 8 Datenleitungen und hier 3 Steuerleitungen.

CE oder Chip enable steuert, ob der Chip überhaupt reagiert. Das wird gleich noch wichtig.

WE Write Enable sagt dem Chip es soll die Daten auf den Datenleitungen speichern,

OE Output Enable gibt den Inhalt aus.

Alle Steuerleitungen sind aktiv low (oder negiert), d.h. um z.B. zu schreiben, müssen wir den Eingang auf 0 setzen.

Über Timing-Dinge machen wir uns erstmal keine Sorgen, wir sind a) im Simulator und b) bei den Taktraten, die wir evtl. mal in echt erreichen würden ist der Chip schnell genug (55ns von Adressauswahl bis Daten bzw. 30ns von OE, beim schreiben sogar einen Tick schneller).

Bei 1MHz Taktrate bräuchten wir +- 1uS, die Chips könnten wir vermutlich mit ~ 8MHz belästigen. Weit mehr als aktuell geträumt. Zur Not muss man ein paar Cent drauflegen und schnellere Chips nehmen.

für den ROM Chip (EEPROM) dann sowas wie der AT28C256-15P, auch hier ein 32K Chip, allerdings mit etwas über 8 Euro deutlich teurer (und langsamer mit 150ns, vermutlich so um die 2MHz).

Funktionsweise beim lesen und Anschluss ist identisch zu obigen RAM. Unser Computer schreibt nicht ins ROM.

Unsere Simulatorwelt

Da wir nun aber simulieren, kümmern uns Zugriffzeiten und Unterschiede zwischen RAM und ROM nur begrenzt.

Es werden hier dann jeweils 16K Chips simuliert, jeweils für RAM und ROM.

Chipauswahl

Nur zur Wiederholung, hier unser geplantes Speicherlayout:

| Anfangsadresse | Endadresse | Adressbereich (binär, obere 8 Bits) | Verwendung |

|---|---|---|---|

| 0x0000 | 0x3fff | 0000 0000 - 0011 1111 | ROM |

| 0x4000 | 0x7fff | 0100 0000 - 0111 1111 | RAM |

| 0x8000 | 0x8fff | 1000 0000 - 1000 1111 | Steuerleitungen für IO/Grafik |

| 0x9000 | 0xbfff | 1001 0000 - 1011 1111 | undefiniert |

| 0xc000 | 0xffff | 1100 0000 - 1111 1111 | Reserviert für Grafik |

Wir brauchen nun eine Logik, die jeweils für den Bereich des RAM und ROM den jeweiligen Chip Enable auf 0 setzt, wenn die richtige Adresse anliegt.

Das Spiel hatten wir ja schon bei der Registerauswahl. Hier allerdings etwas einfacher.

Grundsätzlich können wir sagen: das oberste Bit muss 0 sein und zweitoberste wählt den RAM oder ROM aus.

| A15 | A14 | ROM | RAM |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 |

Mathematisch können wir nun sagen (in programmiertypischer Schreibweise):

ROM = A15 | A14 (A15 oder A14)

RAM = A15 | !A14 (A15 oder (nicht A14) )

Um das ganze billiger zu bauen, kann man nun boolesche Mathematik anwenden und aus 2 Bausteinen (ein Oder und ein Inverter) einen machen. Achtung, etwas hässlich:

ROM = ! ( !A15 AND !A14 ) = !A15 NAND !A14

RAM = ! ( !A15 AND A14 ) = !A15 NAND A14

Das soll billiger sein? Ja, denn wir brauchen einmal ein negiertes A15 und das ist (A15 NAND A15), ein negiertes A14 (A14 NAND A14) und 2x NAND für RAM und ROM. Das macht 4. Genau die Anzahl, die auf einem NAND Chip ist.

Aber da wir später an unser "Chip-Select" Modul noch mehr anhängen wollen, brauchen wir noch mehr invertierte Signale, also sparen wir uns die Optimierung.

Im nächsten Artikel kümmern wir uns dann tatsächlich um die Umsetzung.